As also mentioned in the article, Chinese companies don't always perform the trick to actually scale. It can be to get funded or as a result of funding. The resulting production process isn't under 'control', so it doesn't scale and can't be really be put into practice outside of a laboratory. In case of SMIC they appear to have mastered the trick for this one chip. Doing it for any chip is a more difficult trick to perform. If it was so easy Samsung, which did 8nm on DUV, would have used it on 7nm also. But TSMC, Intel and Samsung all switched to EUV for this 7nm or smaller. So still a very great achievement on DUV, it's probably a one-trick pony that doesn't go any further (production scaling or sub-7nm).

If you think 7nm on DUV is much cheaper, because EUV is so expensive, it might not be.

- High-end DUV equipment reaches EUV costs.

- You need multiple reticle masks (the production step pattern for the wafer) and these costs a lot of money to produce.

- All the additional production steps cost time, money and drastically increase the chance of an error causing you workings chips to be lower. A chip that doesn't work doesn't make you money.

- All additional steps can be so costly in time the production takes way longer (instead of 2 months it's more like 6 months), also increasing the chance of having an outage / maintenance-routine during production (which increases the changes of production issues).

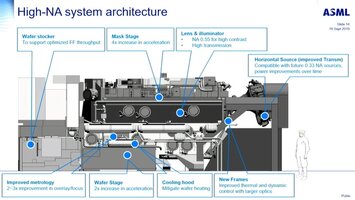

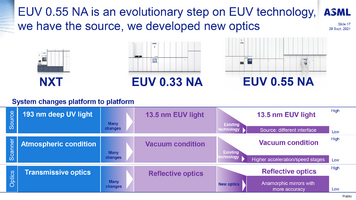

Most of these things are addressed by using EUV. EUV does require a completely new way of working, new factory and new equipment (which is very very expensive). So the initial investment is higher, but the result will be faster and better production. As EUV isn't available in China using DUV is their only option though.